�����x�E���M��������������v�T�[�r�X

���u�̏��^���E���@�\�����i�݁A��̎����v���d�v�ƂȂ��Ă��܂��B

���ʐM����̐��i�J���Ŕ|��ꂽ�����x�E���M��������v�ɂ���J�����ԒZ�k�A�R�X�g�ጸ���������܂��B

- �u���b�N�}/��H�}/�l�b�g���X�g�Ȃǂ̂�����C���^�[�t�F�[�X��������d�l���쐬�A�A�[�g���[�N�v�������Ȃ��A�e��������[�J�[�ɓK�����K�[�o�f�[�^��

- �A�[�g���[�N(�z�u�E�z��)�v�H���Ɠ����i�s���`���g�`�EEMI�V�~�����[�V�������s���A�M�������E���x�̍�����v������

- ���������ɂ�萻���i���̂���Ȃ������͂���A���������̎�߂�����

- ����CAD�x���_�[�̐v���ɑΉ�

���{�P�C�f���X�E�f�U�C���E�V�X�e���Y��(Allegro® PCB Editor)�A������� �}��(CR-5000 Board Designer/CR-8000 Design Force)

�ۑ�

�����E���@�]���H������̎�߂�

���X�����x�E�����w�����i�ފ�����ł́A����ŐV�̐����Z�p�ɓK�����z���d�l�i�M���w�A�d���w�A�\���_�[���W�X�g�A�V���N�Ȃǐ��������j�ɏ��������A�����i����ۏ����A�[�g���[�N�v���d�v�ł��B

�������ɐ��������d�l�ᔽ�����������ꍇ�A���̒i�K�Ŋ�����𒆒f���A�ăA�[�g���[�N�v�E�Ċ�����ƂȂ�H���̎�߂�ƂȂ�܂��B

�܂��A���@�]���H���ł́A�m�C�Y��(EMI)�ɋN��������̔z���s����E�o�����ꍇ������A���̃t�B�[�h�o�b�N�����u�J���������L�v���̈�ƂȂ��Ă��܂��B

![�����E���@�]���H������̎�߂�̐}](/products/packaging_design/image/packaging_design_01.png)

�������@

�����E���@�]���H������̎�߂�}�~

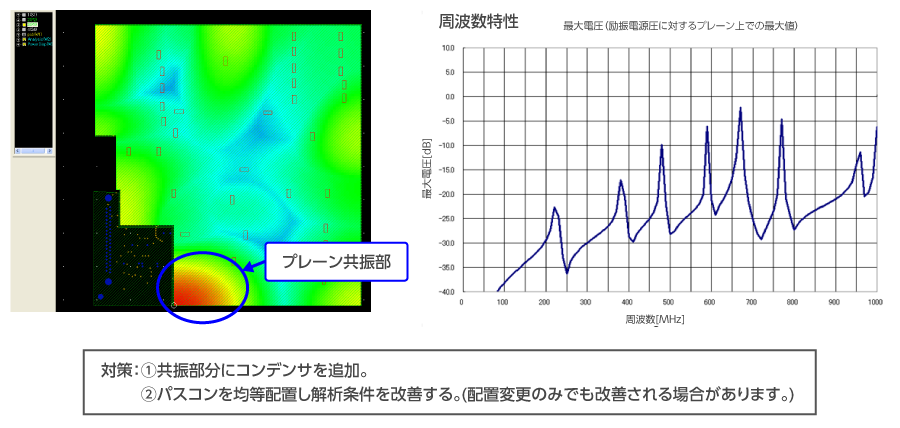

�A�[�g���[�N (�z�u�E�z��)�v�H���Ɠ����i�s�œ`���g�`�EEMI�̃V�~�����[�V�������s���A����E�]���̎�߂���������ƂƂ����M�������E���x�̍�����̎����v���������܂��B

�������͂ɂ�萻���i���̂���Ȃ������͂���A��������̎�߂��������܂��B

![�����E���@�]���H������̎�߂�}�~�̐}](/products/packaging_design/image/packaging_design_03.png)

����

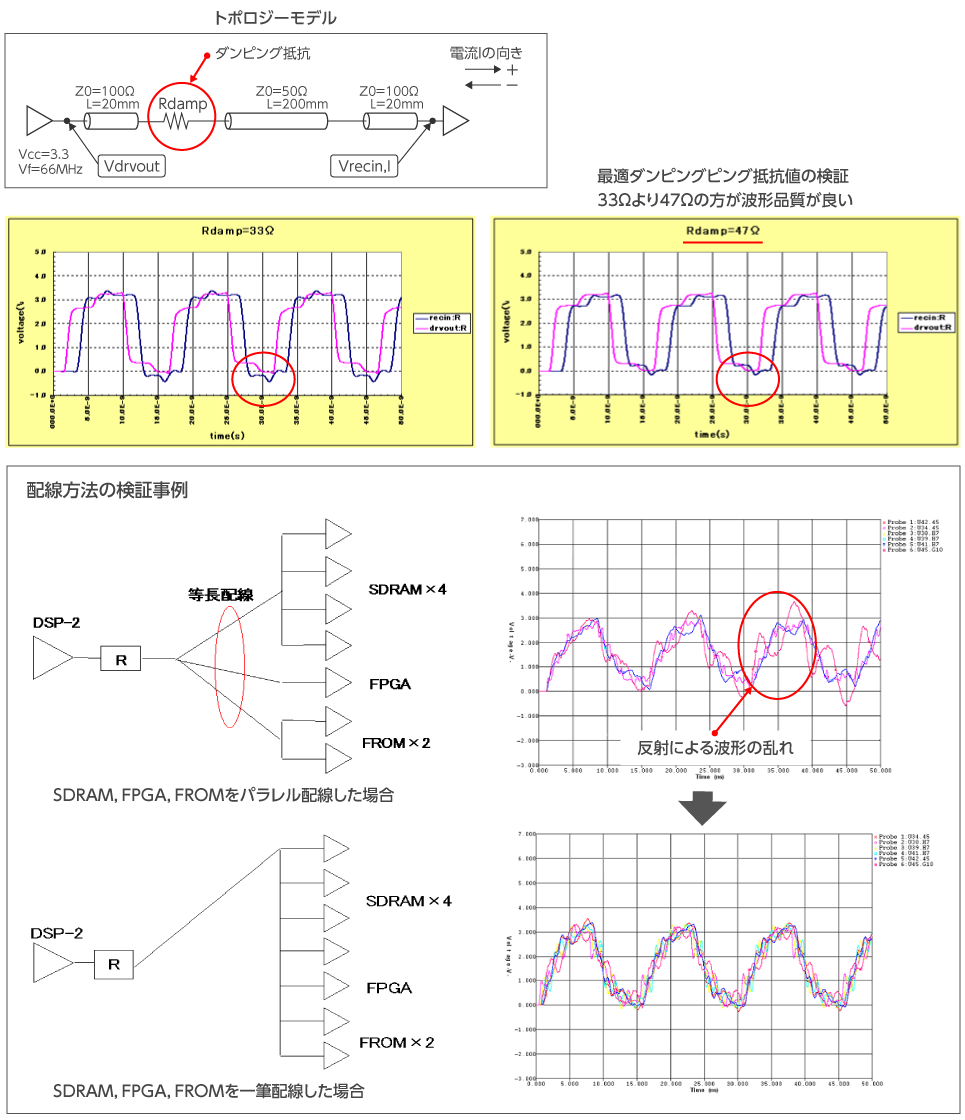

����1�F�`���g�`�V�~�����[�V����

���i���m�̐ڑ�����I�[��R�E�_���s���O���@���A�V�~�����[�V�����ɂĔg�`�m�F���邱�ƂŐM���`���̖��_��������O�ɉ������܂��B

�y�V�~�����[�V�������ڗ�z

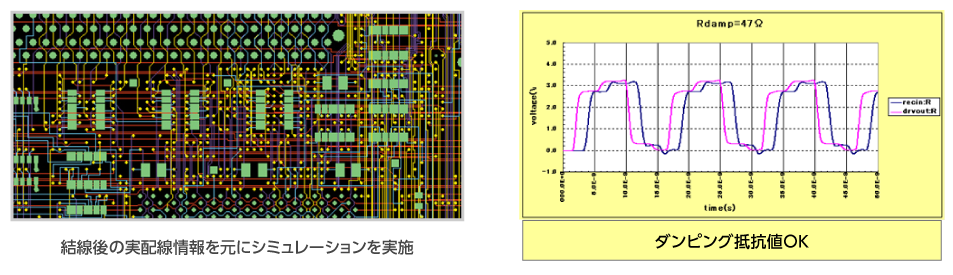

�i1�j��H�}�������ɃV�~�����[�V���������{���M���`���̖��_�𑁊��ɉ����i�@�v��SIM�j

�i2�j������̎��z���������ɃV�~�����[�V���������{���ŏI�g�`���m�F�i�A�|�X�gSIM�j

�@�v��SIM�i�`���V�~�����[�V�������؎���j

�A�|�X�gSIM�i�`���V�~�����[�V�������؎���j

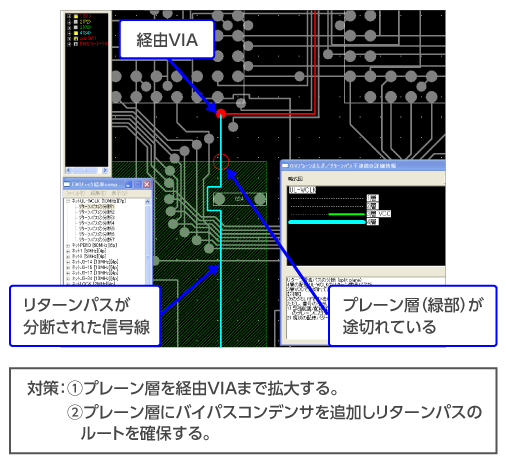

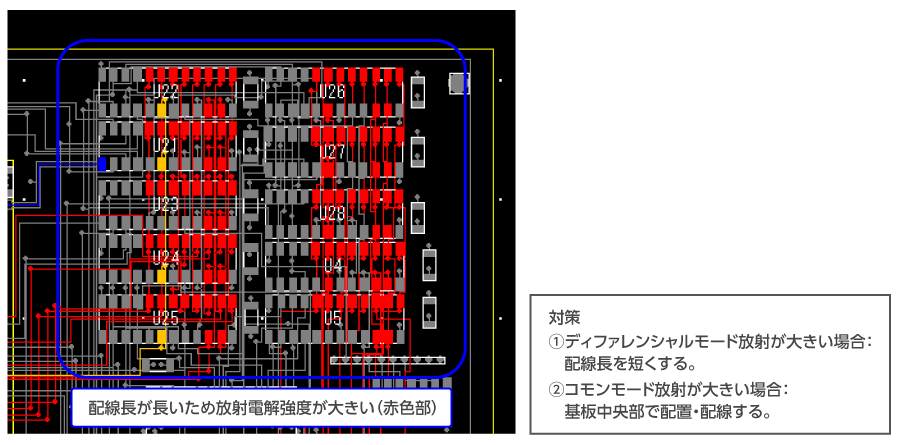

����2�F EMI �V�~�����[�V����(EMI�}���v�x���`�F�b�N�uDEMITASNX�v)

�m�C�Y�̔��������ɂȂ肤�鍀�ڂ��`�F�b�N���A�m�C�Y�����̖��_�����O�ɉ������܂��B

�y�`�F�b�N���ڗ�z

�i1�j�A�H�d�����f�n�`�F�b�N�i�@���^�[���p�X�s�A���`�F�b�N�Ȃǁj

�i2�j�d���n�`�F�b�N�i�A�f�J�b�v�����O�L���p�V�^�`�F�b�N�j

�i3�j�z���n�`�F�b�N�i�B���˓d���`�F�b�N�Ȃǁj

�i4�j�d���E�O�����h�v���[�����U��� �i�C�d���E�O�����h�v���[�����U��͗�j

�@���^�[���p�X�s�A���`�F�b�N

�A�f�J�b�v�����O�L���p�V�^�`�F�b�N

�B���˓d���`�F�b�N

�C�d���E�O�����h�v���[�����U��͗�

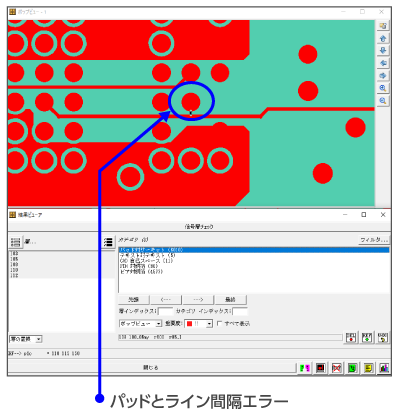

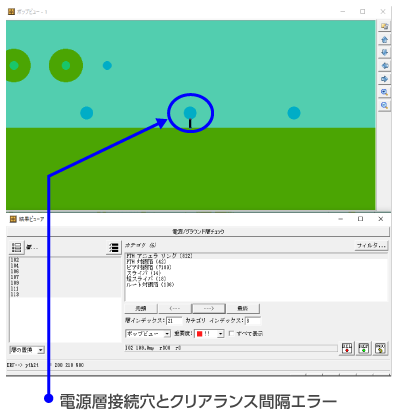

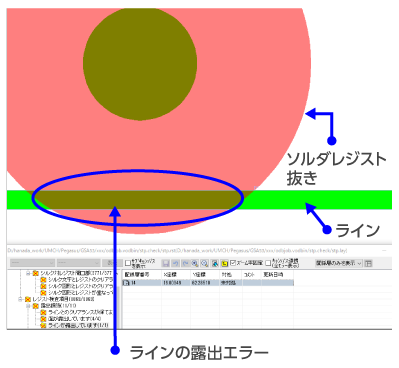

����3�F��������

�A�[�g���[�NCAD�ł͓E�o�ł��Ȃ���������[����̖����A�A�[�g���[�N�v�̒i�K�ʼn�͂����H��(�����)�ł̒��f�E��߂�E������蒼����������܂��B

�y��͍��ڗ�z

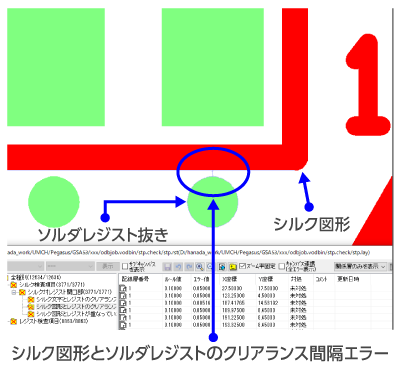

�i1�j�M���w�`�F�b�N�i�@�p�^�[���Ԋu�`�F�b�N�Ȃǁj

�i2�j�d���w�`�F�b�N�i�A�ڑ����ƃN���A�����X�Ԋu�`�F�b�N�Ȃǁj

�i3�j�\���_�[���W�X�g�`�F�b�N�i�B�������`�F�b�N�Ȃǁj

�i4�j�V���N�`�F�b�N�i�C�V���N�ƃ\���_�[���W�X�g�̊Ԋu�`�F�b�N�Ȃǁj

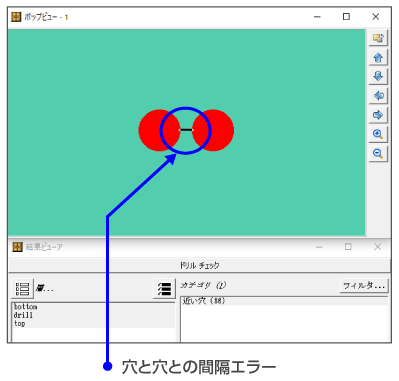

�i5�j�h�����`�F�b�N�i�D���ƌ��Ƃ̊Ԋu�`�F�b�N�j

��͗�@�@�p�^�[���Ԋu�`�F�b�N

��͗�A�@�ڑ����ƃN���A�����X�Ԋu�`�F�b�N

��͗�B�@�������`�F�b�N

��͗�C�@�V���N�ƃ\���_�[���W�X�g�̊Ԋu�`�F�b�N

��͗�D�@���ƌ��Ƃ̊Ԋu�`�F�b�N

��������

| �p�r | ���e(�����A�d�l) | |

|---|---|---|

| LSI�e�X�^�[ | LSI�e�X�^�[�p�p�t�H�[�}���X�{�[�h | �����w(50�w)�A�����`��(�`12Gbps)�AZo�R���g���[�� Pogo/ZIF/LIF�C���^�[�t�F�[�X�A�f�W�A�i���� |

| �l�b�g���[�N�@�� | ���[�^�[�p��@�ق� | �����w(30�w)�A�����`��(�`12Gbps)�AZo�R���g���[�� ���s��LSI������(30��) |

| �T�[�o�[�p�@�� | RAID�@�ق� | �����w(30�w)�A�����`��(�`12Gbps)�AZo�R���g���[�� |

| �Y�Ɨp�@�� | FA�A�摜�f�f���u�@�ق� | USB3.1(Gen2)�APCI-E(Gen3�j�ALPDDR4(3200MHz) SubLVDS�ASLVS�AMIPI-DPHY�A�V���A�� |

| ��×p�@�� | �x�b�g�T�C�h���j�^�[ X���f�f�AMRI�@�ق� |

PCI-E(Gen2) M.2�ATMDS(1.65Gbps)�AmSATA(3Gbps) ARM-CPU(RZ-G1H)�ASH-4�AWLAN���W���[�� |

| �摜�������u | �����摜������@�ق� | PCI-E(Gen2/3)�A�f�W�A�i�ϊ��ADDR4 |

| �d���{�[�h/��H | DCDC�A�d����H | AD�R���o�[�^�[�ADCDC�A�����o�b�e���[�̏[���d�����H |

| �����w��� | �����`����� | |

|---|---|---|

| �w�� | �`50�w | 4�`30�w |

| �� | �`7.3mm | �`3.6mm |

| ���a | ��0.15mm�` | ��0.15mm�` |

| ���C���� | 0.07mm�` | 0.07mm�` |

| ���� | ���s��BGA��\�ʎ����� ���s�b�`CSP�Ȃǂ������\ |

�����g�Ή�(GHz��)�̍ޗ��ɂ��Ή��\ �o�b�N�h�����Ή� |

�T�[�r�X���e

| �H�� | �ݔ��A�c�[���� | �@�\ | ���� |

|---|---|---|---|

| ��H�}���� | Allegro Design Authoring | ��H�}�G�f�B�^ | PCB�f�U�C���v |

| OrCAD® Capture CIS | |||

| CR-8000 Design Gateway | |||

| CAD-CAD�ԕϊ� | Stella Station Translator | Allegro⇔CR8000�ԃf�[�^�ϊ��c�[�� | |

| �A�[�g���[�N | Allegro PCB Editor | �z�u�E�z�� | |

| CR-5000 Board Designer | |||

| CR-8000 Design Force | |||

| CR-8000 DRAGON EX | �����z���c�[�� | ||

| ������̓c�[�� | ValorTM NPI | PCB/PCBA ������� | �����s�ǂ�v�i�K�Ō��� |

| CR-8000 DFM Center | |||

| �V�~�����[�V���� | HyperLynxTM SI | �g�`�V�~�����[�V���� | �g�`�i���̌��� |

| CR-8000 Design Force SI | �g�`�A�N���X�g�[�N��́AFFT �A�A�C�p�^�[����́ATDR��́AFD��� | �v�i�K�ł̋��x�m�F | |

| CR-8000 Design Force PI/EMI | PI�F�����g�C���s�[�_���X��� EMI�F�R�������[�h/IO�J�b�v�����O�m�C�Y���� DC�FIR�h���b�v���� |

||

| EMI�v�x�� �c�[�� |

DEMITASNX | EMC�`�F�b�N�E���U��͂ɑΉ� | �v�i�K��EMC�}�����\ |

| CR-8000 EMC Adviser EX | �p�X�R���A���[�v�A�A���e�i�ȂǁA������H�ɕK�v��EMC�A���^�[���o�H�̃`�F�b�N�A�N���X�g�[�N�\��EMC�g�����[�� |