- ��{�v����V�X�e���]���܂ŁAMBD��@��K�p�����g�[�^���̐v�t���[������

- �������ʐM�G���W�j�A�����O��MBD�m�E�n�E�𗘗p���邱�Ƃɂ��A���q���܂̊J�����Ԃ̒Z�k���x��

�ۑ�

1�d�l�̂����܂����ɂ���ꗂ�����

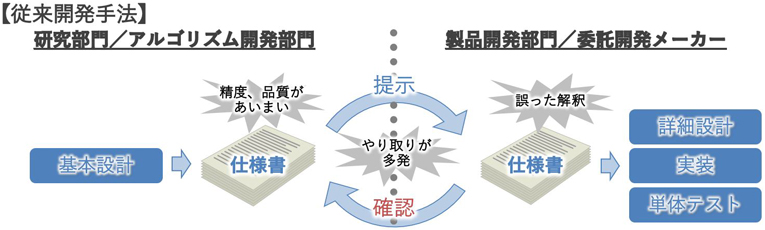

��ƊԁA�g�D�ԁA����Ԃł̎d�l�̎n��������ہA�K�v�Ȑ��x��i�����ݒ肳��Ă��Ȃ��A�����܂��Ȏd�l�ł́A�m�F�̂��߂̂���肪�������A���Ԃ�v���邾���łȂ��A��������߂����Ă��܂����Ƃ�����܂��B

2�����H������̎�߂�̔���

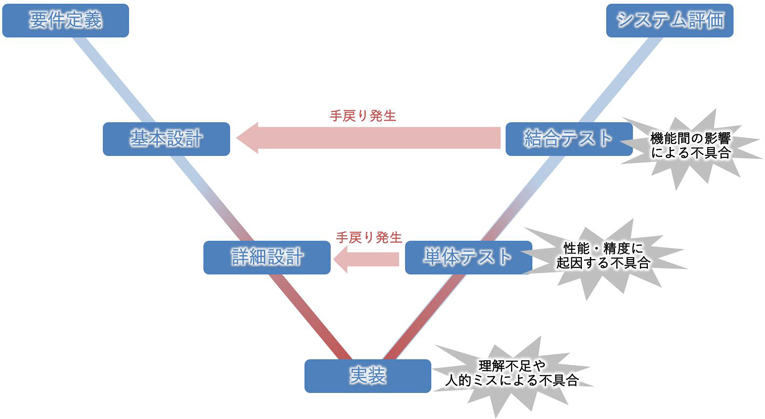

�]���v��@�ł́A�R�[�f�B���O�i�����j��ɏ��߂ē���m�F�����{���邽�߁A�d�l�ɋN������s�������Ǝ�߂肪�������A����ȍH�����K�v�ƂȂ�܂��B

�������@

1���s�\�Ȏd�l�̒ɂ��A�����܂�����r��

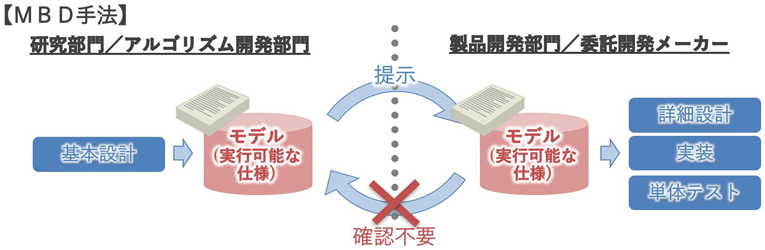

�d�l�n���O�ɁA���f���œ���m�F���邱�Ƃɂ��A�d�l���������܂�����r���ł��A�d�l�m�F�̂���肪�s�v�ɂȂ�܂��B�܂��A�d�l�̒��Ǝ�̑��œ���m�F�ł��邽�߁A�d�l�̗���s���������ł��܂��B

��{�v���ɒ�`�����@�\���f�����A�ڍ���̎������f���ɂĊm�F�ł��܂��B�܂��A�ڍ����ɔ��������������V�X�e���ɂǂ��e�����邩�m�F�ł��܂��B����ɂ��A�J���H���S�ʂɓn��A����������уg���[�T�r���e�B���m�ۂł��A�����Ɏd�l���m�肳���邱�Ƃ��ł��܂��B

- *

-

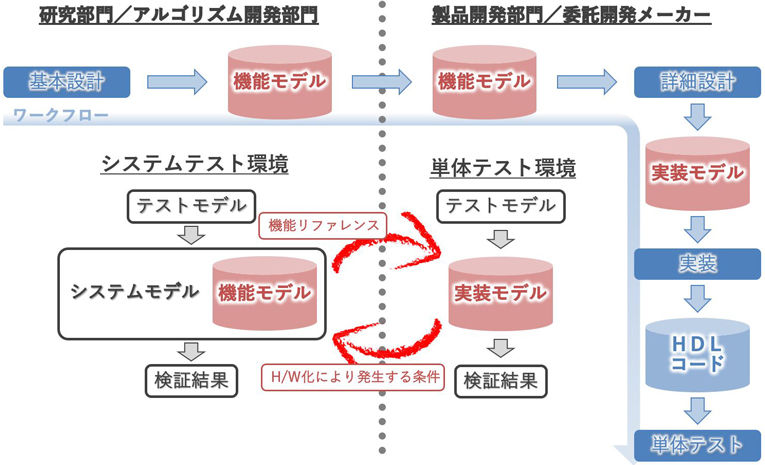

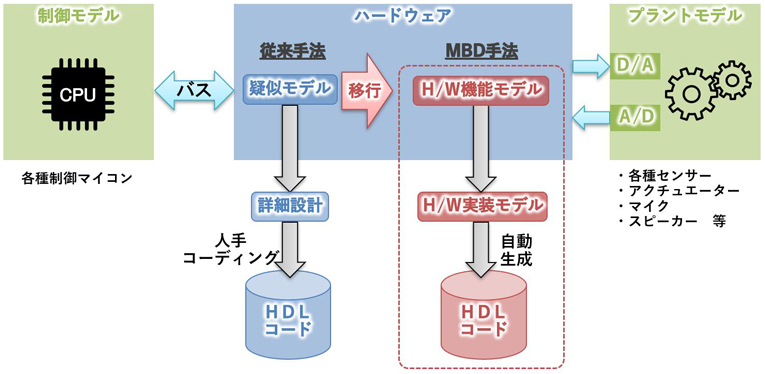

�u�@�\���f���v�FH/W�̋@�\��M����ŋL�q�������f���ł���A�V�X�e���S�̂̌��Ɏg�p�\

�u�������f���v�FSimulink�ŋL�q�������f���ł���A�@�\���f���Ɠ�����HDL�̐������\

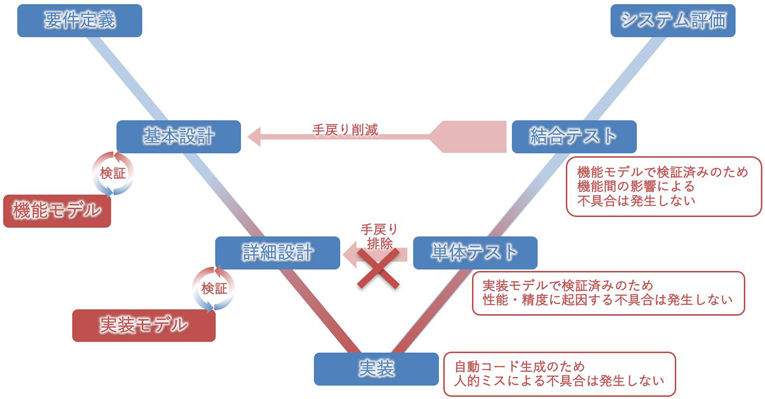

2�㗬�H���ł̌��ɂ�艺���H������̎�߂���팸

�㗬�H���i��{�E�ڍאv�j�ŁA���炩���߃��f���ɂ�蓮����m�F���Ė��_���������邱�ƂŁA�����H���i�P�́E�����e�X�g�A�V�X�e���]���j�ł̎�߂���Ȃ����A�J�����Ԃ�Z�k���܂��B

�܂��A�����R�[�h�����E�������؊��𗘗p���邱�ƂŎ����ƒP�̃e�X�g�̐l�肪�s�v�ƂȂ�܂��B

����

�g�[�^���v�t���[�̂���

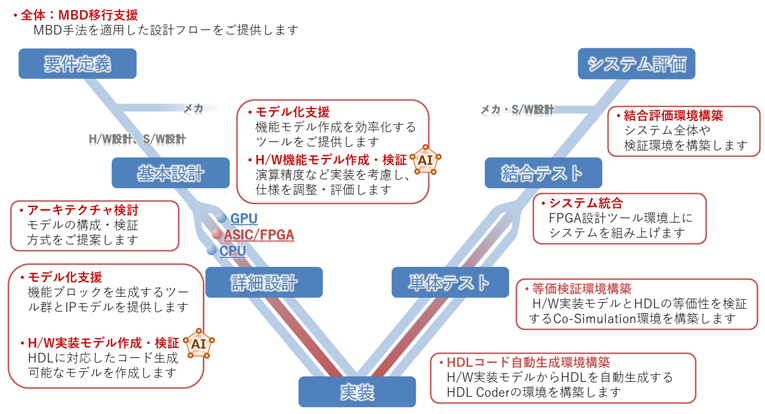

��{�v�t�F�[�Y�ɂ�����A�[�L�e�N�`����������A�@�\���f���쐬�A�������f���쐬�AHDL�R�[�h�����ȍ~�̃V�X�e���]���܂ŁAMBD��@��K�p�����g�[�^���̐v�t���[�������܂��B

MBD�v�t���[

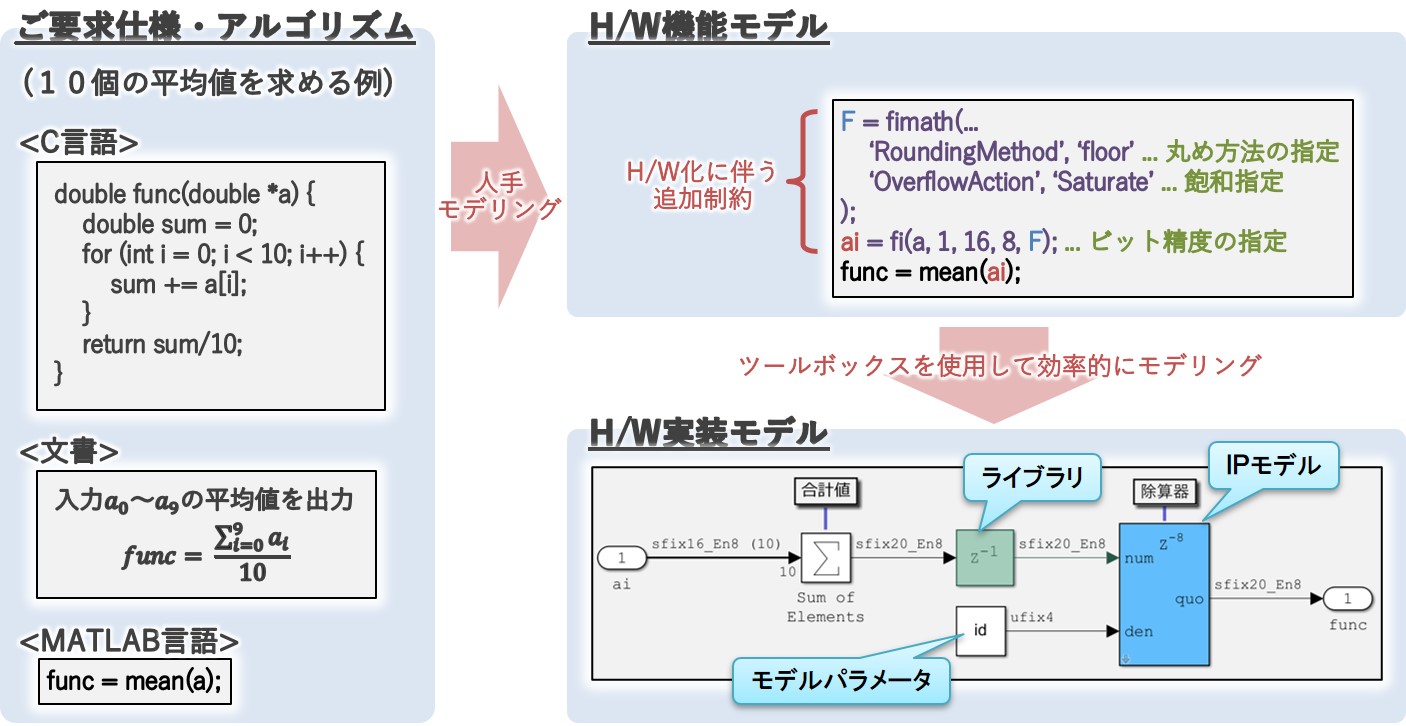

�@�\���f���Ǝ������f��

�@�\���f����H/W�̋@�\��\�������L�����x�̏�ʋL�q�iM����j�ŁA�V�X�e�����A�덷���ς�A�������f���̌��Ɏg�p���܂��B�������f���͋@�\���f���Ƌ@�\�I�ɓ����Ŏ��Ԃ̊T�O���܂݁AHDL�����������\��Simulink���f���i�u���b�N���}�j�ł��B

����AI�����p���āA���i���ȃT���v���R�[�h�̐������A�V�X�g

M�����Simulink�̏ڍׂ́A��������Q�Ƃ��Ă��������B

�������ʐM�G���W�j�A�����O�́A

MathWorks Connections Program �p�[�g�i�[�ł��B

MBD�ڍs�x��

���Ђ�MBD�m�E�n�E���Ïk�����_���v�A���ɍœK�ȃc�[���{�b�N�X�i�c�[���E���C�u�����Q�j�ƁA�e��摜������C���^�t�F�[�X�ڑ���H�쌟�؍ς݂�IP���f���Ƃ��Ē��邱�ƂŁA���q���܂̃X���[�Y��MBD�ւ̈ڍs���x�����A���i���Ȑv�E���؊��������܂��B

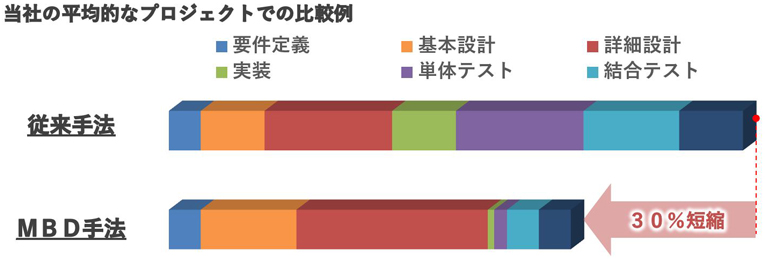

![�]����@��MBD��@�̔�r](/products/mbd/image/mbd_08.jpg)

MBD��@��������邱�Ƃɂ��A�X���[�Y�ȏ��`�B���ł��A�㗬�H���Ŗ��������邽�߁A�����H������̎�߂��啝�ɒጸ�ł��A�g�[�^���̊J�����Ԃ��30���Z�k�ł��܂��B�i���Ў��сj

�c�[���{�b�N�X

���Ђ̃m�E�n�E��MATLAB/Simulink���g�����_���v�ɍœK�ȃc�[���E���C�u�����Q�������܂��B

�{�c�[���{�b�N�X�́AMATLAB�̃A�h�I���Ƃ��ăC���X�g�[���\�ł��B

| No. | �J�e�S�� | ���e | ���� |

|---|---|---|---|

| 1 | ���f���Ǘ� | SimulinkProject�e���v���[�g | �{�e���v���[�g���g�p���邱�ƂŁA�v���W�F�N�g�쐬�Ɠ����ɕK�v�ȃt�H���_�\������уJ�X�^�}�C�Y�\�ȃX�N���v�g�A�t�@�C���ɕt�����邽�߂̕��ރ��x�����p�ӂ���܂��B |

| 2 | ���f���p�����[�^�Ǘ� | ���ރ��x���ƘA�g���ăv���W�F�N�g�̊J�n�I���ɍ��킹�ă��f���ɕK�v�ȃp�����[�^�������I�ɓW�J�E�폜���������܂��B | |

| 3 | HDL�����p�����[�^�Ǘ� | ���W���[�����������f���ɓn��ꍇ�ł��ꊇ���Ăg�c�k�����p�����[�^���Ǘ��ł��������܂��B | |

| 4 | ���f���쐬 | �K�C�h���C�� | ���f���̉ǐ������コ���邽�߂̃K�C�h���C������܂��B�ǐ��̍������f���̍\�z�͕ێ琫�E�ė��p�������������łȂ��A���҂��������₷�����r�����K�ɍs���邱�Ƃŕi������ɂ��d�v�ȗv�f�ƂȂ�܂��B |

| 5 | �v���~�e�B�u�u���b�N | �ǐ����d�������u���b�N����܂��B | |

| 6 | �ƊE�W���o�X�ڑ� | AXI4�EAvalon�o�X�Ɛڑ����邽�߂̃}�X�^�E�X���[�u�C���^�t�F�[�X����܂��B | |

| 7 | ���W�X�^�E���������������E�Ǘ� | �G�N�Z���V�[�g�i���W�X�^�}�b�v�j����C���|�[�g�^�G�N�X�|�[�g���ă��f�����̐��䃌�W�X�^���Ǘ����������܂��B | |

| 8 | �}���`�N���b�N�h���C���Ή� | ���v�ɕK�v�ȃu���b�N����у��f�������c�[������܂��B | |

| 9 | ���f������ | �e�X�g�t���[�����[�N | �e�X�g���s�ɕK�v�ȋ��ʓI�ȏ����������N���X����܂��B������g�p���邱�Ƃɂ��e�X�g���s�X�N���v�g����уe�X�g���ʊm�F�X�N���v�g���Ȍ��ɋL�q�ł���悤�ɂȂ�܂��B |

| 10 | �V�i���I���s���f�� | ���W�X�^�A�N�Z�X�AGPIO�A���荞�݂������CPU�^�����f���ƃ��f���ɗ^����V�i���I�\�z�N���X����܂��B | |

| 11 | �摜�X�g���[�����o�̓��f�� | 2�����̉摜�f�[�^���X�g���[���ɕϊ�����DUT�ɏo�͂�����ADUT����o�͂����X�g���[����2�����̉摜�f�[�^�ɖ߂����f������܂��B | |

| 12 | AXI4�EAvalon-MM�Ό����f�� | �o�[�X�g�]���ɑΉ�����}�X�^����уX���[�u���f�����x�����獂���x���ȃR�}���h�Ő���ł���N���X�����킹�Ē��܂��B | |

| 13 | ���f���������� | �������؊����������c�[�� | �������ɕK�v�Ș_���V�~�����[�^�N����Co-Simulation�ݒ�X�N���v�g�������������܂��B |

IP���f��

�ƊE�W��I/F�iAXI4, Avalon�j�Ɛڑ��\�Ȋe��摜�����_����IP���f���Ƃ��Ă����܂��B

OpenCV�݊�����т��q���ܓƎ��d�l�̘_����v����IP���f���Ƃ��Ă����邱�Ƃ��\�ł��B

| No. | ���� | ���e | ��ȓ��e |

|---|---|---|---|

| 1 | ���ʎd�l �i�摜�����j |

��f�f�[�^�^ | boolean�Auint8�Auint16�i�摜���o�͎��ɃQ�C������уI�t�Z�b�g��������j |

| 2 | �ő�摜�T�C�Y | 1920x1080 | |

| 3 | �J���[�T���v�����O | 4�F4�F4 | |

| 4 | �F��� | �P�F�A2�F�A3�F�A4�F�i3�F�{alpha�j | |

| 5 | �������Z���g�� | 200MHz | |

| 6 | �W��IP �i�t�B���^�����j |

�������i���ρA�K�E�V�A���j | �t�B���^�T�C�Y�F8x8�A�W�����x�Fsfix18_En12 |

| 7 | ��l���i�P�����ρj | 臒l�摜���͂��� | |

| 8 | �C�ӃJ�[�l���E�t�B���^ | �t�B���^�T�C�Y�F8x8�A�W�����x�Fsfix18_En12 | |

| 9 | �����t�H���W�i�c���A���k�A�I�[�v�j���O�A�N���[�W���O�j | �O���[�X�P�[���Ή� | |

| 10 | �W��IP �i�摜�ϊ��j |

�F��ԕϊ� | 3�~3�̍s�Z�{�I�t�Z�b�g�����Z |

| 11 | LUT | �ő�F�[�x�F10�r�b�g | |

| 12 | �W��IP �i�ϊ��j |

�g��k���i�j�A���X�g�E�l�C�o�[�A�o�C���j�A�A�o�C�L���[�r�b�N�ALanczos�j | �T�u�s�N�Z���ʒu����\�F8�r�b�g |

| 13 | �A�t�B���ϊ� | �T�u�s�N�Z���ʒu����\�F8�r�b�g �ő�ϊ������F�����}3��f�A�����}3��f |

|

| 14 | �W��IP �i�摜�����j |

�A���t�@�u�����h | �摜����2�n���A�d�ݓ���1�n���A�摜�o��1�n���A�摜����яd�ݓ��͂�I�� |

| 15 | ��敽�� | �摜����2�n���A�摜�o��1�n���A���v8�F����ʑI�� | |

| 16 | ���́A�������o | �e���v���[�g�}�b�`���O | �T�������FSSD�A�T���͈́F5x5 |

| 17 | HOG�����ʒ��o | �Z���T�C�Y�F10x10, 15x15, 20x20, 25x25, 30x30 �u���b�N�T�C�Y�F3�~3 ���z��������\�F20�x�i9�����j |

|

| 18 | �I�v�V����IP | �u���b�N�}�b�`���O | �T�����@�A�u���b�N�T�C�Y�A�T���͈͂����v�]�ɍ��킹�Č������A�������܂��B |

| 19 | �o�C���e�����t�B���^ | �T�C�Y�F7�~7 �����p�����[�^�F�K�E�V�A���t�B���^�W���A�P�x���W�� ���̑��F�P�x���̎Z�o���x��8�r�b�g�A�W���C���g�o�C���e�����t�B���^�ɑΉ� |

|

| 20 | �I�v�V����IP �iOpenCV�݊��j |

�X�e���I�u���b�N�}�b�`���O �����FStereoBM() |

�u���b�N�}�b�`���O�A���S���Y���𗘗p���ăX�e���I�Ή��_�T�����s���܂��B ���v�]�ɍ��킹�Č������A�������܂��B |

| 21 | �Z�~�O���[�o���u���b�N�}�b�`���O �����FStereoSGBM() |

�Z�~�O���[�o���u���b�N�}�b�`���O�A���S���Y����p���ăX�e���I�Ή��_�T�����s���܂��B ���v�]�ɍ��킹�Č������A�������܂��B |

|

| 22 | �c� �����Fremap() |

�摜�ɑ��Ĕėp�I�Ȋw�ϊ���K�p���܂��B ���v�]�ɍ��킹�Č������A�������܂��B |

|

| 23 | 3D���W�ϊ� �����FreprojectImageTo3D() |

3�������W�_�����e�ϊ���p���ĉ摜���ʂɎˉe���邱�ƂŃV�[���̃r���[���\�����܂��B ���v�]�ɍ��킹�Č������A�������܂��B |

|

| 24 | �C���^�t�F�[�XIP | USB3.0�R���g���[���ڑ� | �ڑ���FCypress�А�USB�R���g���[�� �����o�X�FAXI4�����Avalon-MM�����o�X�ɃA�N�Z�X���邽�߂�PC�A�v���ƕ����Ē��܂��B |

| 25 | SDI | �Ή����[�g�FHD-SDI�A3G-SDI�A12G-SDI ���v�]�ɍ��킹�ăJ�X�^�}�C�Y���Ē��܂��B |

|

| 26 | I2C�C���^�t�F�[�X | �}�X�^����уX���[�u�C���^�t�F�[�X�����v�]�ɍ��킹�ăJ�X�^�}�C�Y���Ē��܂��B | |

| 27 | SPI�C���^�t�F�[�X | 3�E4���V���A�����v�]�ɍ��킹�ăJ�X�^�}�C�Y���Ď������܂��B |

���f���A�g�x��

�]����@�ł͐��䃂�f���ƃv�����g���f����ڑ�����H/W�i�A�i���O�t�����g�G���h�����j�ɂb����Ȃǂ̋^�����f�����g�p���Ă���A�V�X�e���S�̂ł̃��f�������ł��܂���ł����B

���Ѓ\�����[�V�����ł�H/W�Ƃ��ċ@�\���f���������A�V�X�e���S�̂ł̃��f���A�g�����\�Ƃ��܂��B

�T�[�r�X���e

�T�[�r�X���e�̈ꗗ�����̕\�Ɏ����܂��B

| �v�H�� | ���� | ���e |

|---|---|---|

| �S�� | MBD�ڍs�x�� | MBD��@��K�p�����g�[�^���̐v�t���[�������܂� |

| ��{�v | �A�[�L�e�N�`������ | ���q���܂̐��i�d�l�ɑΉ������A�[�L�e�N�`�����������A����Ă��܂� |

| ���f�����x�� | �K�v�ȃc�[���{�b�N�X�������A���q���܂����g�ł�H/W�@�\���f���̍쐬�ƌ����T�|�[�g���܂� | |

| ���f���쐬�E���� | ���q���܂̐��i�d�l�ɑΉ������AH/W�@�\���f�����쐬���A�����܂� | |

| ���f���A�g�x�� | H/W�@�\���f���������A�V�X�e���S�̂ł̃��f���A�g�����T�|�[�g���܂� | |

| �ڍאv | ���f�����x�� | �K�v�ȃc�[���{�b�N�X��IP���f���������A���q���܂����g�ł�H/W�������f���̍쐬�ƌ����T�|�[�g���܂� |

| ���f���쐬�E���� | H/W�@�\���f�������t�@�����X�Ƃ���H/W�������f�����쐬�E�����܂� | |

| ���� | HDL�R�[�h�������\�z | H/W�������f������HDL��������������HDL Coder�̎��s�����\�z���܂� |

| �P�̃e�X�g | �������؊��\�z | H/W�������f���Ǝ�����������HDL�̓�������������Co-Simulation�̎��s�����\�z���܂� |

| �����e�X�g | �V�X�e������ | ��������HDL�t�@�C����IP�����AFPGA�����c�[�����g�p�����V�X�e���̑g�ݏグ���T�|�[�g���܂� |

| �����]�� | �g�ݏグ���V�X�e���S�̂ł̌��؊����\�z���܂� | |

| �V�X�e���]�� | ���@�]�� | ���@�]�����T�|�[�g���܂� |

��������

�摜�����֘A

�摜��������Ƃ��ċ@�B�w�K�A���J����A�A�i���O�E�f�W�^�����݊J���ł��K�p���т�����܂��B

| No. | ���� | �J���T�v | ���q���܂���� �C���v�b�g |

���{���e | �������� |

|---|---|---|---|---|---|

| 1 | �Y�� |

�ΏہF�f���������u FPGA�F�S��iStratix V�j |

�v���d�l�� �A���S���Y�� �i�d�l���x�[�X�j |

�@�\���f���Ǝ��@����̓����������� | �摜�̃o���G�[�V�����m�F�ɂ����āASimulation�̑���Ɏ��@���g�p���ASIM���s���Ԃ�80%�ጸ |

| 2 | �Y�� |

�ΏہF�摜�������u FPGA�F�U�� �iStratix V�j |

�v���d�l�� �A���S���Y�� �iC�x�[�X�j |

�V�X�e�����f����I/F����у������ш挩�ς��� | �v�����i�K�őg�ݍ��킹���쎞�̑ш挟���\�Ƃ��A�v�߂�H����20%�ጸ |

| 3 | ���� |

�ΏہF�@�B�w�K���u FPGA�F�P�� �iCyclone IV�j |

�v���d�l�� �A���S���Y�� �iC�x�[�X�j |

CPU�����̈ꕔ��H/W�����Ƀ|�[�e�B���O���č����� | �菑�������̔F���������x��20�{�Ɍ��� |

| 4 | �ԍ� |

�ΏہF�X�e���I�摜�������u FPGA�F�P��iStratix V�j |

�v���d�l�� | OpenCV��H/W���E�A�v������P�̌Ăяo�� | OpenCV����HD����i1080p@60fps�����j�̃��A���^�C������������ |

| 5 | ��� |

�ΏہF���J����V�X�e�� FPGA�F�P��iCyclone IV�j |

�v���d�l�� ���䃂�f�� �@�\���f�� �v�����g���f�� |

���f���A�g�x���i�������f�����V�X�e�����f���ɑg�ݍ��݁j �Œ菬���_�� |

�]���̓f�W�^���������^�����f���i�A�����f���j�ŃV�X�e�����f���������{���Ă������A���ۂ̓���Ɠ����Ȏ������f���ɓ���ւ��邱�ƂŃV�X�e�����f���Ńf�W�^�����i�Œ菬���_���E���U���j�̉e���]�������� |

| 6 | ��� |

�ΏہF�J�����摜�������u FPGA�F�Q��iKintex7�AKintex UltraScale�j |

�A���S���Y�� �i�d�l���x�[�X�j |

������46�A����T���W���[����IP�Ƃ��ĒA�@�\���f�����V�X�e�����f���ŗ��p | Xilinx�А�Vivado��IP Integrator��IP�Ƃ��Ē��邱�Ƃł��q���ܑ��ł̎��R�ȃV�X�e���g�ݏグ�E���O���������� |

| 7 | �Y�� | �ΏہF�A�i���O�E�f�W�^������IC |

�v���d�l �@�\���f���� |

�A�i���O�E�f�W�^�����݃��f�����A�Œ菬���_�� | �f�W�^�����̌Œ菬���_���ɑ���A�i���O�����܂߂��`�b�v�S�̂ւ̉e����IC�����O�Ɍ��ς邱�Ƃ��\ |

| 8 | �ԍ� |

�ΏہF�X�e���I�摜�������u FPGA�F�P��iMPSoC�j |

�ύX�d�l�� ����RTL |

����RTL���W���[���̉��ł�����MBD�ւ̈ڍs���x�� | ����RTL�Ƃ̑Δ�ɂ��MBD�̗L�����𗝉����������A�܂����q���ܑ��ł�MBD�ɂ��p���J�������� |

| 9 | �Y�� |

�ΏہF�Y�Ƌ@�����FPGA �iAXI�o�X�ڑ�IP�j |

�v���d�l�� | ����IP�iAXI�ڑ����W�X�^�����������f���j��AXI�X�g���[���摜�����̃T���v�����f������AMBD�ւ̈ڍs���x�� | MBD�̋�̗�̒ɂ��A���q���ܑ��ł�MBD������ |

�����ʐM�֘A

�����ʐM�֘A�ŁA�ȉ��K�p���т�����܂��B

| No. | ���� | �J���T�v | ���q���܂���� �C���v�b�g |

���{���e | �������� |

|---|---|---|---|---|---|

| 1 | �S�� |

�ΏہF���A���^�C���X�y�N�g�����@�� FPGA�F�P��iStratix �W�j |

�v���d�l�� | �M�������A���S���Y�������f���ɂ����f�[�^��́A�A���S���Y�������f���Ǝ������f���̐������̊m�F | �A���S���Y�����퐫�̌��X�s�[�h�̌���ƌ�H���ւ̃X���[�Y�Ȏd�l�W�J |

| 2 | �ʐM |

�ΏہFWiMAX2�ϒ����u �iOFDM�ϒ����f���j |

�v���d�l�C���[�W�A �ʐM�K�i |

�A���S���Y�������f���Ǝ������f���̐v�Ɛ������̊m�F | ��{�v�i�K�ł̃��f�����r���[�̎��{�ɂ���߂�̍팸 |

| 3 | ���� |

�ΏہFTVWS OFDM�ϕ������u FPGA�F�P��iStratix �W�j |

�v���d�l�� | �M�������A���S���Y�������f���ɂ����f�[�^��́A�A���S���Y�������f���Ǝ������f���̐������̊m�F | �A���S���Y�����퐫�̌��X�s�[�h�̌���ƌ�H���ւ̃X���[�Y�Ȏd�l�W�J |

| 4 | ���� |

�ΏہF����������X�g���[�W���u FPGA�F�S��iVirtex7�j |

�A���S���Y�� �im�t�@�C���j |

���q���܃A���S���Y����H/W�� | m�t�@�C���ł̂����ɂ��d�l�̔F���̍��ق��팸 |

| 5 | �ԍ� |

�ΏہF���x�v�p�h�b�v���[���[�_���u FPGA�F�P��iCyclone V�j |

�A���S���Y�� �im�t�@�C���j |

���q���܃A���S���Y���̃��f�����iH/W,S/W�j�A�܂����f�[�^�ɂ���͎x�� | m�t�@�C���ł̂����ɂ��d�l�̔F���̍��ق��팸�A�܂��A���S���Y���ύX���̌�H���܂ł̐v���Ԃ�Z�k |

| 6 | ���� |

�ΏہF�\�i�[�p�ʐM���� FPGA�F�P��iArtix7�j |

�A���S���Y�� �im�t�@�C���j |

���q���܃A���S���Y���̃��f�����iH/W,S/W�j | m�t�@�C���ł̂����ɂ��d�l�̔F���̍��ق��팸�A�܂��A���S���Y���ύX���̌�H���܂ł̐v���Ԃ�Z�k |

| 7 | ���� |

�ΏہFIEEE802.11a Wi-Fi���C�NOFDM�ϕ������u FPGA�F�P��iZynq UltraScale+�j |

�v���d�l���A �ʐM�K�i |

�A���S���Y�������f���Ǝ������f���̐v�Ɛ������̊m�F | ��{�v�i�K�ł̃��f�����r���[�̎��{�ɂ���߂�̍팸 |

| 8 | �Y�� |

�ΏہF�����x��������шʒu����V�X�e�� FPGA�F�P��iZynq7000�j |

�v���d�l�� | �A���S���Y�������f���Ǝ������f���̐v�Ɛ������̊m�F | �A���S���Y�����퐫�̌��X�s�[�h�̌���ƌ�H���ւ̃X���[�Y�Ȏd�l�W�J |

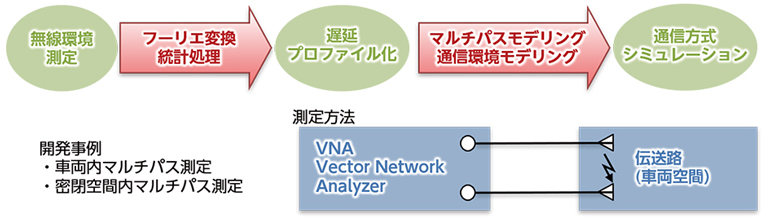

�����������f�����O��������

�ʐM�@����g�p��������ɂ����āAVNA��p���Ď��g�������𑪒肵�A�x���v���t�@�C�������s�Ȃ��܂��B

���̌��ʂ���Ƀ}���`�p�X���f�����쐬���A�����������ʐM�����V�~�����[�^��ō\�z���邱�Ƃɂ��A�ʐM�����̍œK���V�~�����[�V�������\�ƂȂ�܂��B