高信頼FPGA設計

ミッションクリティカルな用途や、機能安全規格*の認証が必要な製品では、搭載されるFPGAにも高信頼性が求められます。

日立情報通信エンジニアリングは長年培った確かな技術と経験で、FPGAの課題を解決します。稼働を止めることができない重要なシステムや業務を強固に支えるために、次に示すような技術を提供しています。

- 宇宙線中性子によるソフトエラーの対策技術

- エラーの伝搬を確実に制御するアイソレーション実装

- 中性子照射試験のサポート・ソフトエラー対策のコンサルティング

- 主な対象

- インダストリー、自動車、ヘルスケア、サーバー・ストレージ、通信・放送、交通、IoT、セキュリティ

- *

- 機能安全規格については「機能安全規格 認証取得支援・開発サービス」を参照してください。

課題

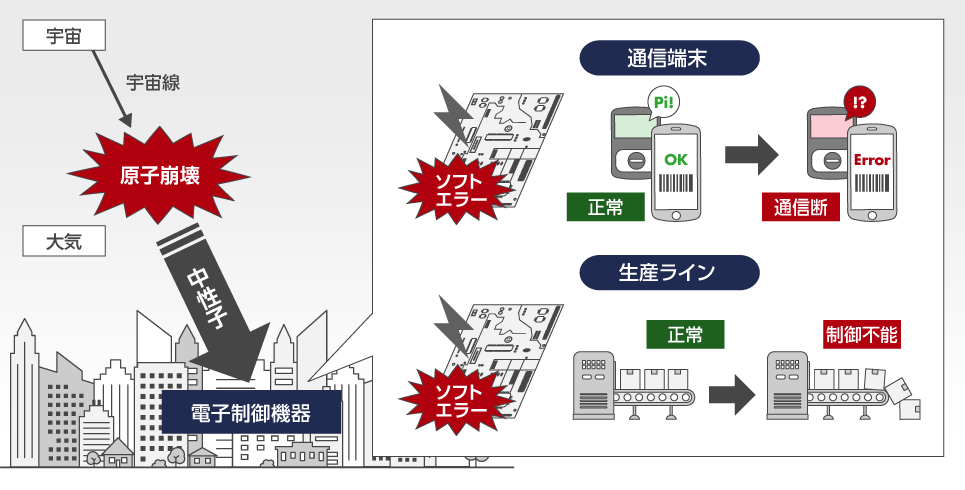

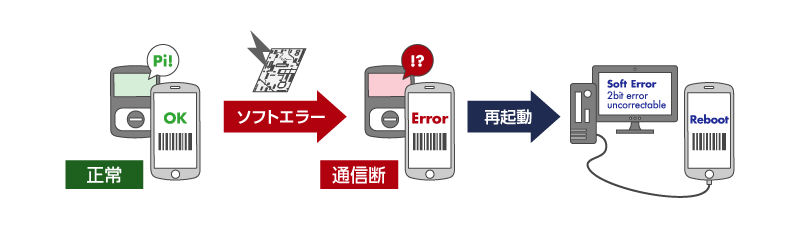

1宇宙線中性子によるソフトエラー

宇宙線中性子の影響によって、FPGA内のコンフィギュレーションRAM(CRAM)の内容が反転し、回路構成が変更されることで発生した機器の誤動作をソフトエラーと呼びます。

ソフトエラーが発生すると、CRAMは電源を再投入しない限り、誤動作を繰り返します。また、電源を再投入して正常な状態に戻ると、誤動作の原因を特定できなくなる問題も起こっています。

FPGAに関するソフトエラーの詳細は、こちらも参照してください。

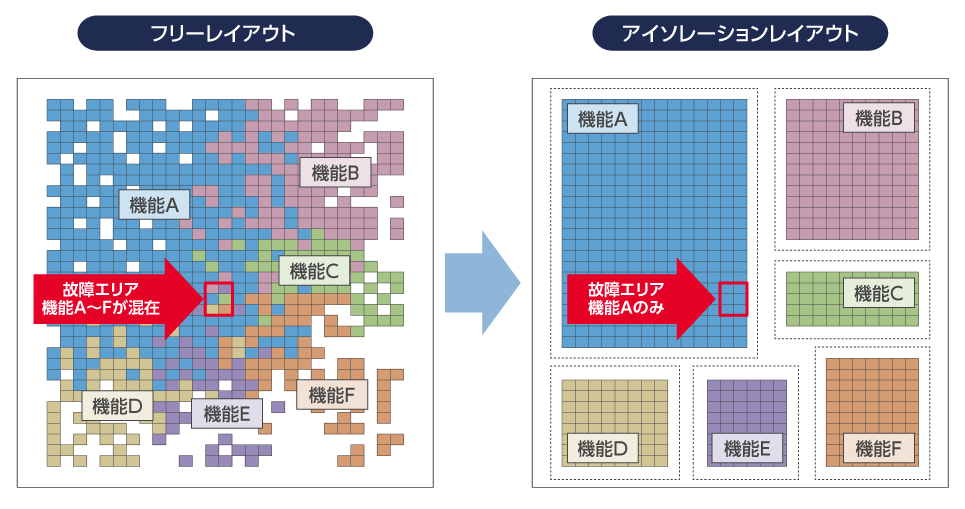

2レイアウトに起因するエラーの伝搬

信頼性と安全性を重視するアプリケーションでは、フェールセーフ要件および物理的セキュリティ要件が求められます。これらの要件を満たすには、エラー伝搬の抑止が不可欠です。

一般的に、FPGAの実装は、ASICのような機能モジュール単位でレイアウトされていません。このため、複数の機能モジュールのゲートや配線が隣接していることがあります。このような状態で物理的な故障が発生した場合、同時に複数の機能にエラーが伝搬するおそれがあります。

解決方法

1ソフトエラー対策機能の搭載

ソフトエラーの対策方法やIPは、各FPGAベンダー(ザイリンクス社、インテル社)から提供されています。ただし、ベンダー提供のIPは仕様が難解で、FPGAの構造を理解していないと組み込みが困難です。

2010年ごろから日立製作所の研究所とともにソフトエラー対策に取り組んできた当社は、長年培った技術と経験で、ベンダー提供のIPを組み込み、「ソフトエラー対策機能」を搭載できます。この機能を使用することで、反転してしまったCRAMのソフトエラーを訂正してシステムを継続したり(ソフトエラー訂正)、ソフトエラー検出でシステムを安全に停止したりできます(ソフトエラー検出)。

2エラーの伝搬を抑止するアイソレーション実装

当社では、エラー伝搬の抑止が必要な製品のFPGAに対して「アイソレーション実装」を行います。

「アイソレーション実装」とは、機能モジュールごとに分離するレイアウトのことです。ゲートや配線を壁(Fence)の内部に閉じ込め、ほかの機能モジュールとの混在を抑止することで、エラーの伝搬を抑止できます。

特長

ソフトエラーに対する独自の技術

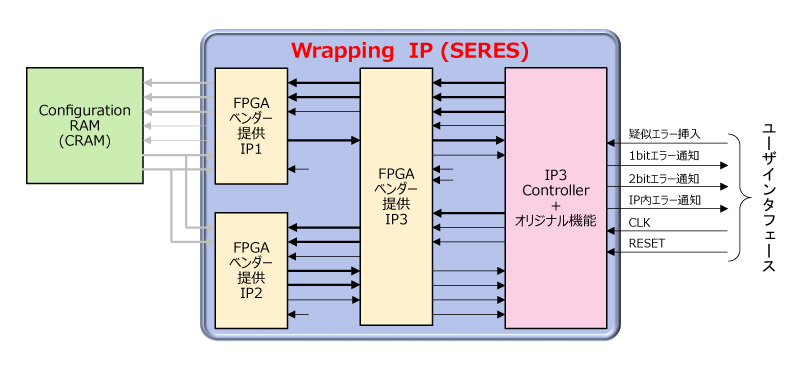

Wrapping IP

長年の技術の蓄積に基づき、ソフトエラー対策機能を容易に組み込むためのWrapping IPを開発しています(ザイリンクス社IPのみ対応)。Wrapping IPにはエラーインジェクション機能も搭載されており、仮想的なソフトエラーを発生させることができます。

ソフトエラー対策 Wrapping IP(SERES*1)

*1 SERES:Soft Error Restoration Support

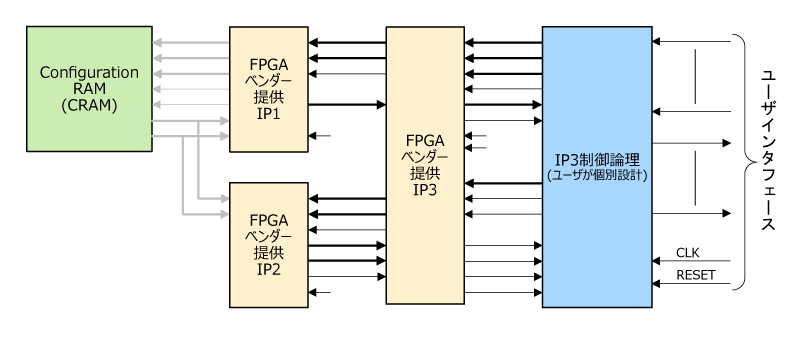

Configuration RAM(CRAM)のソフトエラー対策はFPGAベンダーからIPが提供されています。ソフトエラー対策IPを使用した際の回路構成を図1に示します。IP1〜IP3の接続はユーザが行います。更にIP3を制御するための制御論理はユーザが設計して組み込む必要があります。そのため、各IPの機能、インタフェース、使用方法を正しく理解して設計しなければ、ソフトエラー対策を実現することはできません。

図1 ベンダ提供ソフトエラー対策IPを使用した回路構成

図1 ベンダ提供ソフトエラー対策IPを使用した回路構成

当社は、長年の技術蓄積により、FPGAベンダー提供IPとIP制御論理を一体化した、Wrapping IPを開発しました(図2参照)。このWrapping IPはソフトエラー対策として以下に示す機能を持ち、IPの難しい制御を容易化しました。

Wrapping IP機能

- (1)CRAMの1bit/2bitエラー通知

- (2)CRAMの1bitエラー訂正通知

- (3)CRAMの2bitエラー訂正不可通知

- (4)CRAMの1bit/2bit疑似エラー挿入

- (5)Wrapping IP内の自己故障通知(*2)

- (6)Wrapping IP内の自己故障疑似エラー挿入(*2)

*2 本IPが備える高信頼性を追求したオリジナル機能

図2 当社開発のWrapping IP

図2 当社開発のWrapping IP

ソフトエラーログ機能

FPGAでソフトエラーが発生すると、システムの再起動によって、FPGAが初期化されてしまうため、異常発生の原因を特定できません。当社では、ソフトエラーログ機能を組み込むことで、システムが再起動された状態でもソフトエラーの発生を記録できます。

ソフトエラーログ機能

システムの停止や再起動の原因がソフトエラーによるものか判断するためには、ソフトエラー対策によって検出されたエラー結果を確実に記録する必要があります。しかし、再起動するとFPGAは初期化されてしまうため、検出された結果が消えてしまいます。

当社では、システムが再起動してもソフトエラーを検出した結果を記録すことができる、ソフトエラーログ機能を開発しました。ソフトエラーログ機能は以下に示す特長を持っています。

ソフトエラーログ機能の特長

- (1)再起動(電源再投入)となった場合でもソフトエラー検出結果を記録

- (2)ソフトエラーが発生した日付、時間などの情報も合わせて記録可能

- (3)アイソレーション実装と組み合わせることで、ソフトエラー発生個所の特定が可能

- (4)ソフトエラー対策 Wrapping IPを適用した場合、Wrapping IP内の故障も記録可能

当社のソフトエラー対策のノウハウについてはこちらも参照してください。

ソフトエラー対策のノウハウ

1. ソフトエラー対策してもソフトエラーは発生する

FPGAのソフトエラー対策とは、ソフトエラーの抑止や発生頻度を下げるものではありません。中性子線によりデータ反転を起こしたConfiguration RAM(CRAM)のデータを訂正することです。ソフトエラーは起こるものと認識する必要があります。

2. ソフトエラー対策をしてもシステム誤動作は発生する

FPGAのソフトエラー対策はCRAMのデータ反転を監視し、ソフトエラーが発生してから該当箇所のデータ訂正を行います。そのため、ソフトエラーが発生してから訂正までの時間に誤動作する可能性があります。システムを止めることなく継続稼働させるためには、FPGAのソフトエラー対策だけでなく、システムレベルでのエラー対策を検討して組み込む必要があります。

3. ソフトエラー対策は事前検討が重要

通常の状態でソフトエラーを意図的に発生させることはできないため、組み込んだソフトエラー対策論理が動作するかを確認することは非常に困難です。実機評価で動作確認をするためには、疑似的にソフトエラーを発生させる機能を組み込むことが必要です。また、ソフトエラーによりシステム再起動となっても、ソフトエラーが発生した記録を残すためのログ機能を組み込むことが必要です。これらの機能はシステム要件に沿って、事前に検討することが重要です。

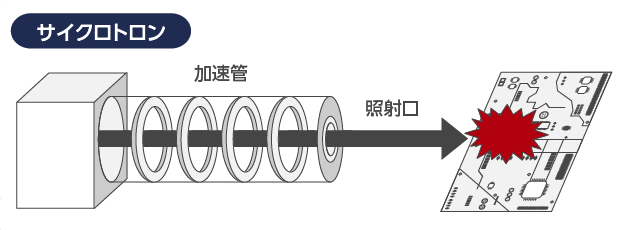

中性子照射試験のサポート・ソフトエラー対策のコンサルティング

製品に対するソフトエラーの影響を確認する方法として、大学機関等が保有する粒子加速器設備を使用した中性子照射試験サービスを日立製作所とともに提供しています。

当社では、中性子照射試験のサポート、およびFPGAのソフトエラー対策に関するコンサルティングや設計を受託しています。

| 試験計画策定 |

|

|---|---|

| 試験作業・分析 |

|

| 対策・設計 |

|

当社は、一般社団法人 量子アプリ社会実装コンソーシアム(QASS)に参画している株式会社

日立製作所の研究開発グループとともにQASSの活動に協力しています。

サービス内容

対応可能なFPGAの概要と、当社独自のサービスについて次の表に示します。

| 対応可能なFPGAの概要 | |||||

|---|---|---|---|---|---|

| FPGAベンダー | ザイリンクス社 | インテル社 | |||

| 対応デバイス |

|

|

|

||

| FPGA開発ツール | Vivado | Quartus Prime | |||

| 設計言語 |

|

||||

| エンジニアリングサービス | |||||

| ソフトエラー検出 | ○ | ○ | ○ | ||

| ソフトエラー訂正 | ○ | ○ | × | ||

| アイソレーション実装 | ○ | ○ | ○ | ||

| 当社独自のサービス | |||||

| Wrapping IP提供 | ○ | × | × | ||

| ソフトエラーログ機能 組み込み |

○ | ○ | ○ | ||

| 中性子照射試験 * | ○ | ○ | ○ | ||

(凡例) ○:対応可 ×:対応不可

- *

- 中性子照射試験は、ベンダーに限らずさまざまなデバイスに対応します(FPGA、RAM、ROM、CPUなど)。

導入事例

国際標準に基づくFPGA開発(通信装置)

地上の通信装置については国際標準が制定されています。当社は、通信装置の国際標準に基づいたFPGAの開発実績があります。

通信装置のソフトエラー対策、ITU-T国際標準制定

引用元:日立製作所 ニュースリリース