LSIはもちろん、FPGA設計においても、実機評価前の論理品質が開発期間に大きな影響を与えます。論理品質確保のためには、指標を用いた論理品質の評価・監視と解析性の高い検証環境が重要です。

日立情報通信エンジニアリングでは、検証計画の提案から、検証環境構築、検証実行まで、一貫したサービスをご提供することにより、お客さまの論理品質確保と開発期間短縮を実現いたします。

課題

半導体プロセス技術の進歩に伴い設計規模が増大しており開発期間も長期化しています。 LSI/FPGAの設計工程における論理検証の割合は、7割を超えていると言われており検証効率の向上が必要です。

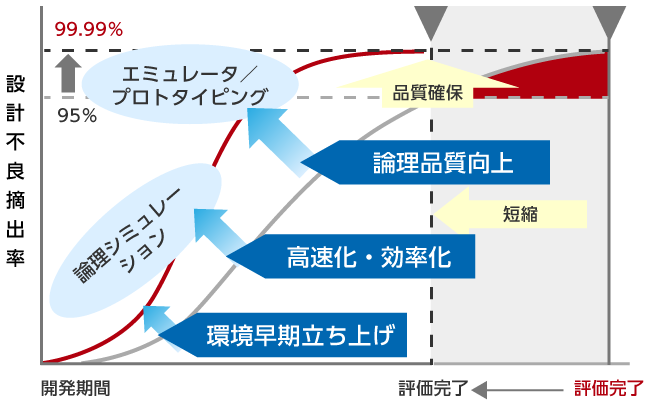

検証期間の短縮には、検証環境の早期立ち上げ、検証の高速化/効率化、論理品質向上の三つの観点からアプローチすることが重要です。

解決方法

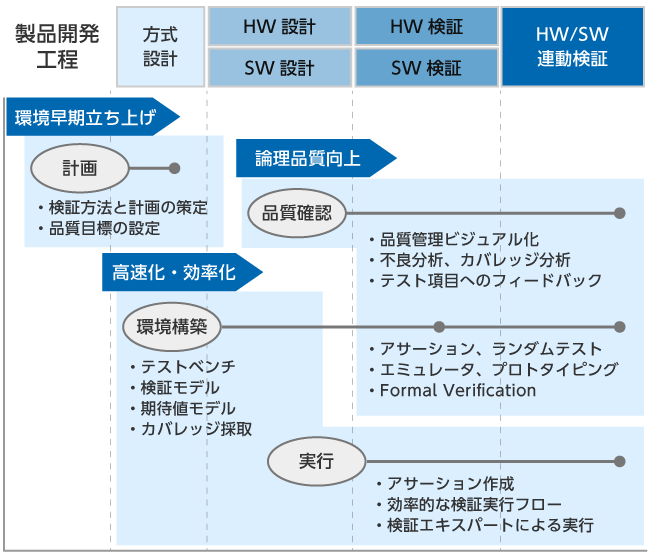

品質確保と期間短縮のためには、検証工程前に計画を策定し、最適な検証環境を構築して、論理品質を確認しながら実行することがポイントになります。

特長

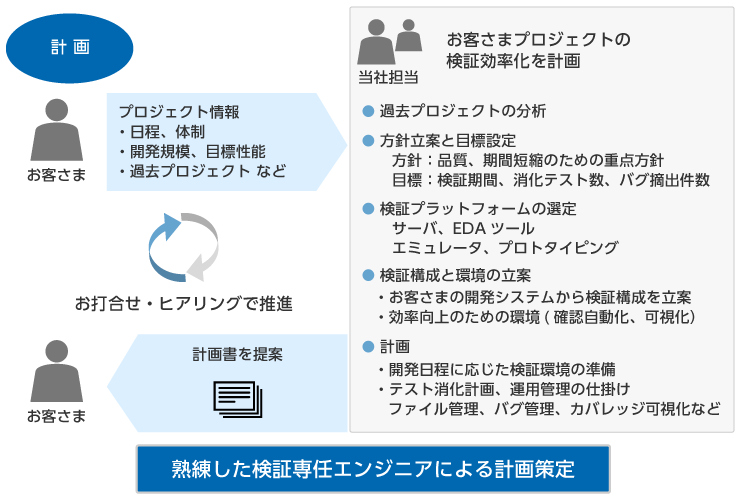

お客さまからプロジェクト情報をいただき、過去プロジェクトの分析、方針立案と目標設定、検証プラットフォームの選定、検証構成と環境の立案などを行い、お客さまプロジェクトの検証効率化を計画します。

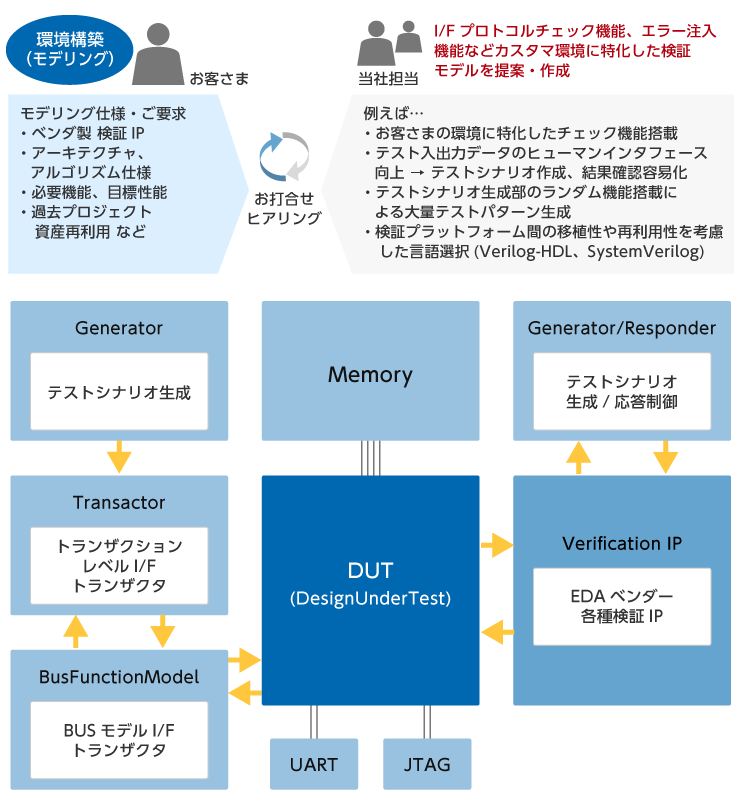

お客さまからモデリング仕様などのご要求をいただき、EDAベンダーの各種検証IPも活用しテストシナリオ生成/応答制御機能、トランザクタなどカスタマ環境に特化した検証モデルを提案します。

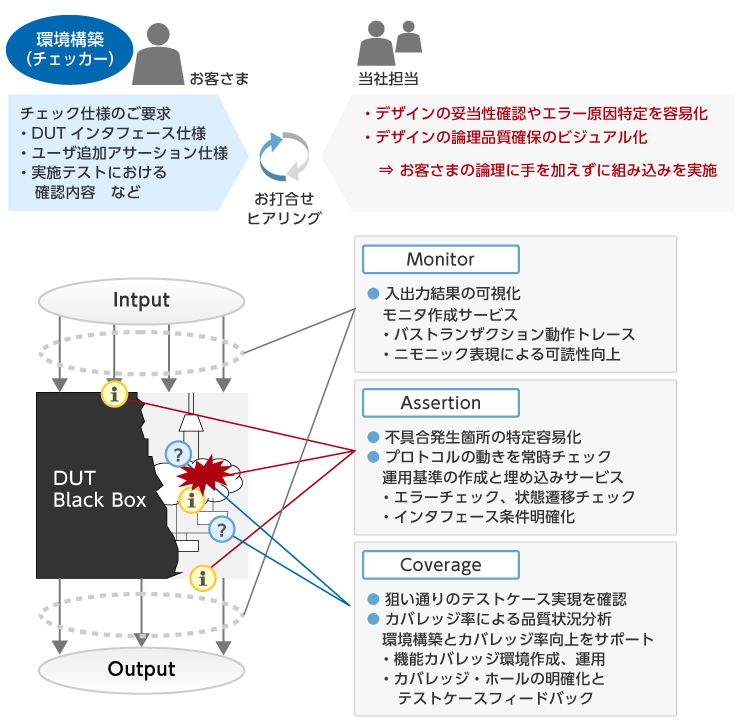

お客さまからチェック仕様のご要求をいただき、デザインの妥当性確認やエラー原因特定の容易化、デザインの論理品質確保のビジュアル化など、Monitor、Assertion、Coverageを駆使しお客さまの論理に手を加えずに組み込みを実施します。

サービス内容

| 分類 | 実施内容・OUTPUT |

|---|---|

| 計画 |

過去の豊富な経験からお客さまに合った検証計画を策定

|

| 環境構築 |

計画に基づきテストベンチ、検証モデル、実行環境、期待値モデル、カバレッジ環境、などを構築

|

| 実行・ 品質確認 |

検証計画に基づき検証を実行

|

導入事例

| 提供先 | 適用環境およびサポート機能 | 効果 |

|---|---|---|

| 電子機器メーカー A社様 |

|

|

| 半導体メーカー B社様 |

|

|

| 半導体メーカー C社様 |

|

|

| 電子機器メーカー D社様 |

|

|